As quantum computing advances toward real-world applications, one of the greatest challenges is mitigating environmental noise. While significant progress has been made in developing superconducting quantum processors, the delicate nature of qubits makes them vulnerable to various error mechanisms. Our recent study on transmon qubits identifies a critical yet often overlooked source of error in two-qubit CZ gates—charge-parity switching caused by quasiparticles.

This research not only sheds light on the problem but also offers a solution through optimised qubit design. Let’s explore what this means for the future of superconducting-based quantum computing.

Superconducting transmon qubits are widely used in quantum processors because of their robustness against charge noise. However, no qubit design is immune to all types of errors. One significant issue arises from quasiparticles, electron-like excitations that can tunnel through the qubit’s Josephson junction, causing a charge-parity switch.

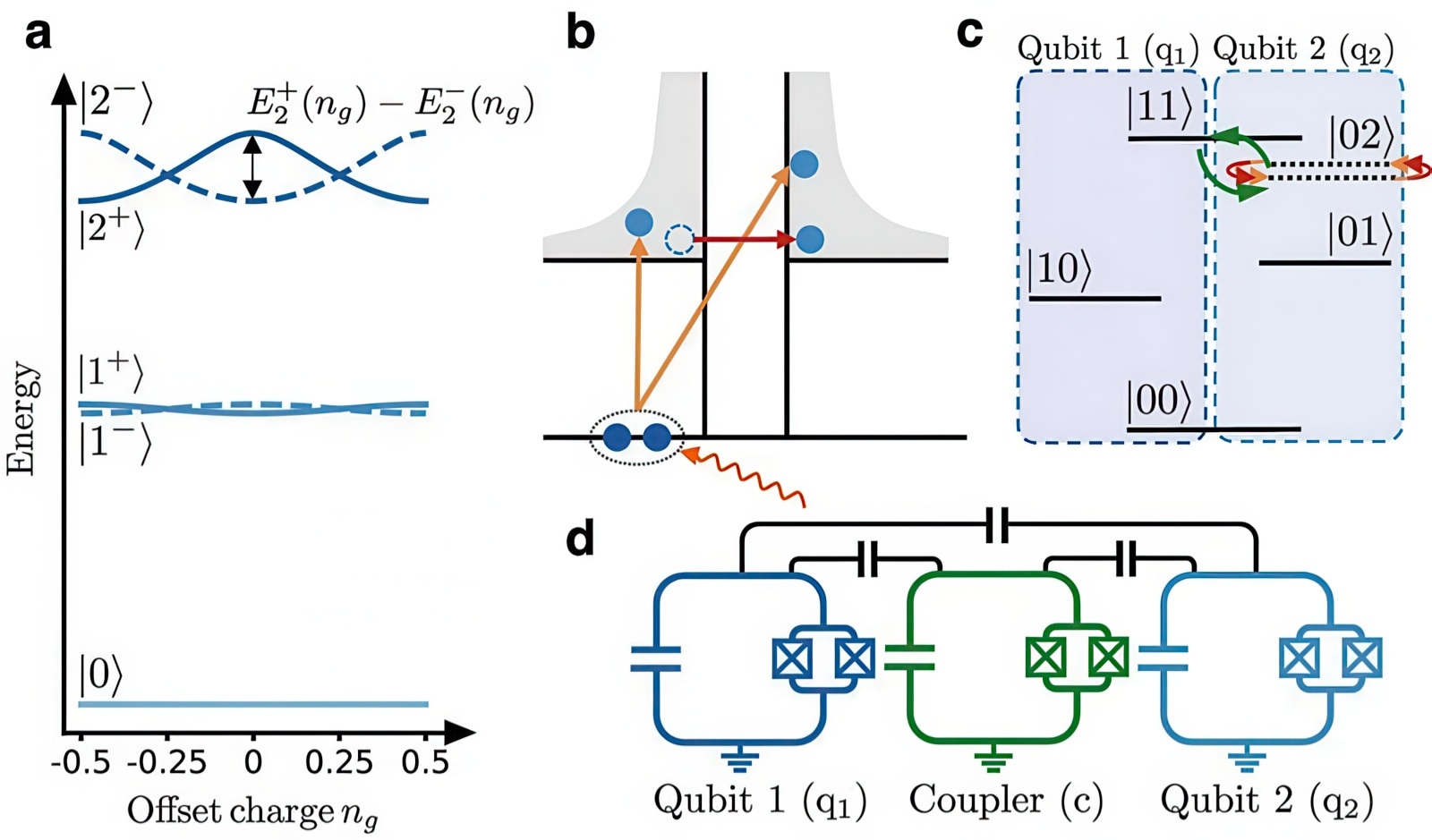

When a quasiparticle tunnels, it alters the charge-parity of the qubit, which shifts its energy levels. Crucially, this energy shift becomes exponentially larger at higher energy levels. In two-qubit gates, such as the CZ gate, the second excited state of the transmon qubit plays a key role. A charge-parity switch can significantly change the energy of this second excited state, directly affecting the conditional phase of the gate and leading to phase errors that degrade the fidelity of the operation.

Figure 1. a the schematic energy diagram of a transmon qubit with two distinct parity manifolds, marked with + and −. While the ground state |0⟩ also comprises of two distinct parity levels, the difference between them is not visible. b Illustration of two parity switching mechanisms. c the energy level diagram of the states involved in the operation of a diabatic CPHASE gate. The Rabi oscillation between the levels |11⟩↔|02⟩ is marked with green arrows, however the larger charge dispersion of the second excited state means that both parity states of the |02⟩ level cannot be considered degenerate. d the lumped element model of the tunable-coupler circuit used in the implementation of diabatic CPHASE gates.

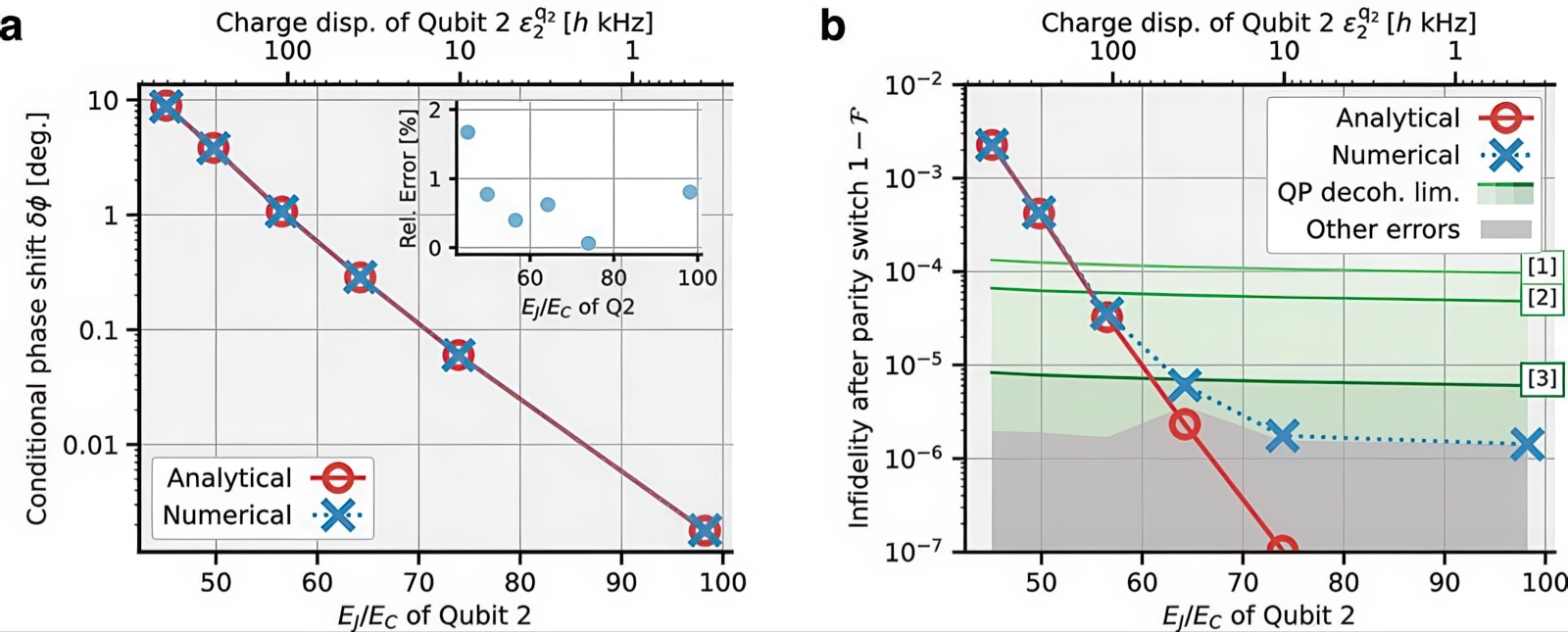

Our research shows that the impact of these errors decreases as the ratio of the qubit’s Josephson energy to charging energy (E_J / E_C) grows. However, determining the optimal design parameters also requires considering other dominant noise processes.

Figure 2. a Analytical predictions (red circles) of the conditional-phase difference of the CZ gate between the two parities. The inset displays the relative absolute error between the analytical predictions and the numerical results. The x-axis represents the 𝐸𝐽𝐸𝐶⁄ ratio (bottom) and second excited state charge dispersion (top) of the qubit with the higher frequency (Qubit 2). b Gate infidelity after a parity switch on Qubit 2, where the theory predictions (red circles) only take into account the effect on the conditional phase. The green lines are estimates of the upper bound for the infidelity contribution of quasiparticle induced decoherence on the two-qubit gate system, with the parity lifetimes measured by different references. The gray area is the region in which errors due to unwanted transitions during the gate operation are more prominent and the effect of a parity switch is negligible. It therefore represents the lower bound of the infidelity, which is largely independent of the ratio 𝐸𝐽𝐸𝐶⁄.

Quasiparticle-Induced Idling ZZ Error

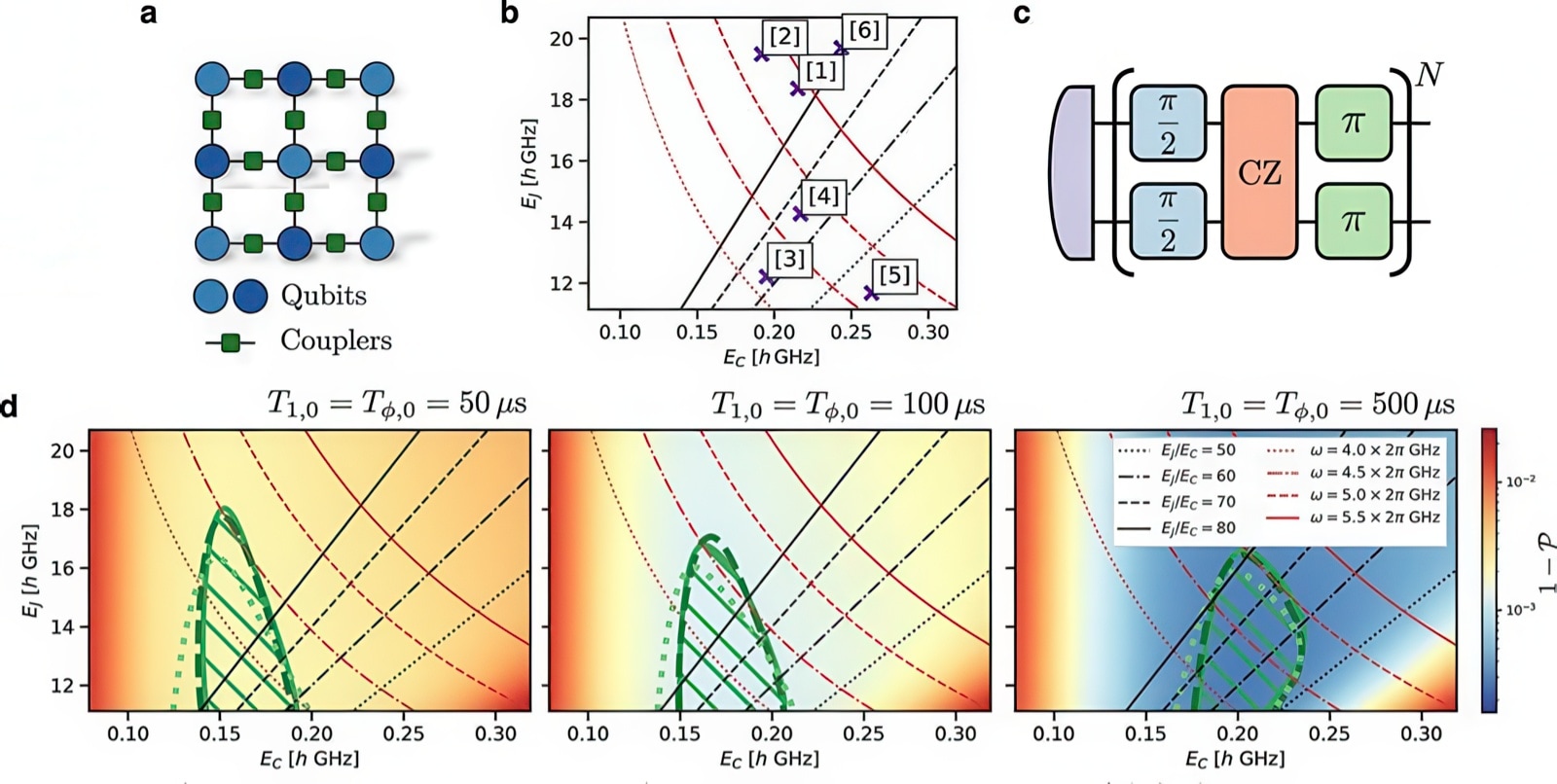

Another key issue addressed in this study is the emergence of quasiparticle-induced idling ZZ error in tunable-coupler architectures. While tunable couplers are designed to eliminate unwanted qubit interactions during idle periods, the stochastic nature of charge-parity switching introduces a residual, always-on ZZ interaction.

This interaction arises because charge-parity switches alter qubit energy levels, creating slight frequency mismatches even when qubits are supposedly decoupled. As a result, an uncontrolled phase can accumulate during idle times, degrading the fidelity of subsequent operations. This error becomes more significant as coherence times extend into the millisecond range, highlighting the need for mitigation in future quantum processors targeting high gate fidelities and complex circuits.

A New Metric for Optimizing Transmon Qubit Design

One exciting contribution of this study is the introduction of a performance metric for quantum circuit execution. This metric helps optimise qubit design parameters by minimising the net effect of quantum errors. It takes into account not only the fidelity and number of single- and two-qubit gates in an algorithm but also the state preparation fidelity and errors due to charge-parity switches.

By balancing the trade-offs between different error sources, our team at IQM identified an optimal range of design parameters for qubits. Fabricating quantum processors within this range reduces errors from charge-parity switching while addressing other key factors like coherence time and state preparation, ultimately enhancing overall performance

Figure 3. a Schematic representation of the square grid architecture, with high- (dark blue) and low-frequency (light blue) transmons, connected via tunable couplers (green). b design parameters of Qubit 2 (q2) from different experimental implementations of the tunable coupler transmon architecture. c Schematic representation of the considered quantum circuit. d 1 – performance metric plotted for different values of the second (higher frequency) transmon design parameters. We consider a single-qubit gate implemented with a Gaussian DRAG pulse with a duration of tSQG = 16 ns, a two-qubit gate duration of tTQG = 50 ns and three different reference coherence times indicated on top of each panel. The striped green area marks the region in which the performance metric is maximized.

Looking ahead: designing for the next generation of quantum processors

As quantum computing technology matures, qubit designs must evolve to minimise all potential error sources, including charge-parity switching. Our study provides key insights into how engineers can better design transmon qubits by fine-tuning critical parameters to enhance the overall processor performance.

With coherence times pushing into the millisecond range and beyond, understanding and mitigating quasiparticle-induced errors will be essential for the reliability and scalability of quantum computers. The performance metric introduced in this study offers a robust framework for navigating the complex trade-offs involved in designing qubits capable of high-fidelity operations.

Download the paper here:

Dr. Amin Hosseinkhani is a Senior Quantum Engineer at IQM Quantum Computers and serves as the Scientific Project Lead for the QSolid consortium. His current research focuses

on developing error mitigation strategies for quantum algorithms and modeling and analyzing noise at the hardware level. During his PhD at Forschungszentrum Jülich, Amin investigated quasiparticle effects in superconducting qubits. He later conducted device modeling and noise analysis for semiconductor spin qubits in silicon during his postdoctoral research at the University of Konstanz. In his spare time, he enjoys hiking, cycling, and playing table tennis.

Search faster—hit Enter instead of clicking.